# Stereo Vision IP Core

Data Sheet

(IP Version 4.6.0) November 7, 2019

Nerian Vision GmbH Zettachring 2 70567 Stuttgart Germany

Email: service@nerian.com www.nerian.com

CONTENTS CONTENTS

# Contents

| 1 | Intr                   | oducti        | ion                                     | 4  |

|---|------------------------|---------------|-----------------------------------------|----|

| 2 | Fea                    | tures         |                                         | 4  |

| 3 | Bac                    | kgroui        | nd                                      | 5  |

|   | 3.1                    | _             | ra Alignment                            | 5  |

|   | 3.2                    | Image         | Rectification                           | 5  |

|   | 3.3                    | Camer         | ra Calibration                          | 6  |

|   | 3.4                    | Dispar        | rity Maps                               | 6  |

| 4 | Ste                    | reo Vis       | sion Core Functionality                 | 9  |

|   | 4.1                    | Image         | Input and Output                        | 9  |

|   | 4.2                    | Rectif        | $ication \dots \dots \dots \dots \dots$ | 10 |

|   | 4.3                    | Image         | e Pre-Processing                        | 10 |

|   | 4.4                    | Stereo        | Matching                                | 10 |

|   | 4.5                    | Cost V        | Volume Post-Processing                  | 11 |

|   |                        | 4.5.1         | Subpixel Optimization                   | 11 |

|   |                        | 4.5.2         | Uniqueness Check                        | 12 |

|   |                        | 4.5.3         | Consistency Check                       | 12 |

|   | 4.6                    | Dispar        | rity Map Post-Proc                      | 12 |

|   |                        | 4.6.1         | Texture Filtering                       | 12 |

|   |                        | 4.6.2         | Speckle Filtering                       | 13 |

|   |                        | 4.6.3         | Gap Interpolation                       | 13 |

|   |                        | 4.6.4         | Noise Reduction                         | 13 |

| 5 | $\mathbf{D}\mathbf{M}$ | A Cor         | re Functionality                        | 13 |

|   | 5.1                    | Ports         | Connected to SVC                        | 13 |

|   | 5.2                    | Interfa       | ace Ports                               | 14 |

|   | 5.3                    | Input         | Formats                                 | 15 |

|   |                        | $5.\bar{3}.1$ | 8-Bit Monochrome                        | 15 |

|   |                        | 5.3.2         | 12-Bit Monochrome LSB Packed            | 15 |

|   |                        | 5.3.3         | 12-Bit Monochrome GEV Packed            | 15 |

|   |                        | 5.3.4         | 12-Bit Unpacked                         | 16 |

|   |                        | 5.3.5         | 8-Bit RGB                               | 16 |

|   |                        | 5.3.6         | 8-Bit Bayer Pattern                     | 16 |

|   | 5.4                    | Outpu         | it Format Conversion                    | 17 |

|   |                        | 5.4.1         | 12-Bit Packed Output                    | 18 |

|   |                        | 5.4.2         | 12-Bit Split Output                     | 18 |

|   |                        | 5.4.3         | 16-Bit Output                           | 18 |

| 6 | Cus                    | tomiza        | ation                                   | 19 |

|   | 6.1                    | SVC (         | Customization Parameters                | 19 |

|   | 6.2                    |               | Core Customization Parameters           | 22 |

|   |                        | 6.2.1         | General Settings                        | 23 |

|   |                        | 6.2.2         | DMA Settings                            | 23 |

| 7 | Sup                    | portec        | d Devices                               | 24 |

CONTENTS CONTENTS

| 8  | Timing                                                | 24        |

|----|-------------------------------------------------------|-----------|

| 9  | Resource Usage                                        | <b>25</b> |

| 10 | IO Signals                                            | 26        |

| 11 | Registers                                             | 30        |

|    | 11.1 DMA Core Registers                               | 32        |

|    | 11.1.1 0x00: Control                                  | 32        |

|    | 11.1.2 0x04: Status                                   | 34        |

|    | 11.1.3 0x08: Image Size                               | 34        |

|    | 11.1.4 0x0C: Output Address Higher 32 Bits            | 35        |

|    | 11.1.5 0x10: Output Address Lower 32 Bits             | 35        |

|    | 11.1.6 0x14: Output Bytes Available                   | 35        |

|    | 11.1.7 0x18: Output FIFO Info                         | 35        |

|    | 11.1.8 0x1C: Left Input Address Higher 32 Bits        | 36        |

|    | 11.1.9 0x20: Left Input Address Lower 32 Bits         | 36        |

|    | 11.1.100x24: Left Input Bytes Available               | 36        |

|    | 11.1.110x28: Right Input Address Higher 32 Bits       | 36        |

|    | 11.1.120x2C: Right Input Address Lower 32 Bits        | 36        |

|    | 11.1.130x30: Right Input Bytes Available              | 36        |

|    | 11.1.140x34: Input FIFO Info                          | 37        |

|    | 11.1.150x38: Rectification Map Address Higher 32 Bits | 37        |

|    | 11.1.160x3C: Rectification Map Address Lower 32 Bits  | 37        |

|    | 11.1.170x40: Rectification Map FIFO Info              | 37        |

|    | 11.1.180x44: Buffer Address Higher 32 Bits            | 37        |

|    | 11.1.19 0x48: Buffer Address Lower 32 Bits            | 38        |

|    | 11.1.20 0x4C: Buffer FIFO Info                        | 38        |

|    | 11.1.21 0x50: DMA Errors                              | 38        |

|    | 11.1.220x58: IP Version Number                        | 38        |

|    | 11.2 SVC Registers                                    | 38        |

|    | 11.2.1 0x00: Control                                  | 38        |

|    | 11.2.2 0x04: Image Size                               | 40        |

|    | 11.2.3 0x08: Algorithm Parameters 1                   | 40        |

|    | 11.2.4 0x0C: Algorithm Parameters 2                   | 40        |

|    | 11.2.5 0x10: License Key Higher 32 Bits               | 41        |

|    | 11.2.6 0x14: License Key Middle 32 Bits               | 41        |

|    | 11.2.7 0x18: License Key Lower 32 Bits                | 41        |

|    | 11.2.8 0x1C: Device DNA Higher 32 Bits                | 41        |

|    | 11.2.9 0x20: Device DNA Middle 32 Bits                | 41        |

|    | 11.2.100x24: Device DNA Lower 32 Bits                 | 41        |

|    | 11.2.11 0x28: SVC Errors                              | 42        |

|    | 11.2.12 0x2C: SGM Penalties                           | 42        |

|    | 11.2.13 0x30: Subpixel Optimization ROI Offset        | 42        |

|    | 11.2.14 0x34: Subpixel Optimization ROI Size          | 43        |

|    | 11.2.15 0x38: IP Version Number                       | 43        |

|    | 11.2.160x3C - 0x90: Debugging Registers               | 43        |

|    |                                                       | 10        |

CONTENTS CONTENTS

| 12        | Reference Design                                                          | 43 |

|-----------|---------------------------------------------------------------------------|----|

| <b>13</b> | Control Flow                                                              | 44 |

|           | 13.1 One-Time Initializations                                             | 44 |

|           | 13.2 Per-Frame Control Flow                                               | 46 |

|           | 13.3 Result Retrieval                                                     | 46 |

| <b>14</b> | Migrating from Previous Versions                                          | 46 |

|           | 14.1 Migrating from Version 4.5                                           | 46 |

|           | 14.2 Migrating from Version 4.3 to 4.4                                    | 47 |

|           | 14.3 Migrating from Versions $4.0 - 4.2$ to $4.3 \dots \dots \dots \dots$ | 47 |

|           | 14.4 Migrating from Version 3.x to $4.0 \dots \dots \dots \dots \dots$    | 47 |

#### 1 Introduction

The Stereo Vision Core (SVC) performs stereo matching on two grayscale or RGB input images. The images are first rectified to compensate for lens distortions and camera alignment errors. Stereo matching is then performed by applying a variation of the Semi Global Matching (SGM) algorithm as introduced by Hirschmüller (2005). Various post-processing methods are applied to improve the processing results. The output of the SVC is a subpixel accurate and dense disparity map, which is streamed over an AXI4-Stream interface.

To simplify the use of the SVC on devices with a shared system memory, such as the Xilinx Zynq SoC, an auxiliary core for direct memory access (DMA) is provided. This DMA core reads input data from memory through AXI3 or AXI4, and converts it into data streams that are suitable for the SVC. Likewise, the DMA core also collects the output data from the SVC and writes it back to memory.

Both IP cores are provided as encrypted RTL code. An IP block for each core is available for Xilinx Vivado IP Integrator.

## 2 Features

The SVC and DMA core comprise the following features:

- General processing architecture

- Processing of grayscale images with a bit depth of 8 or 12 bits per pixel

- Processing of color images with 8-bit RGB or Bayer pattern encoding

- $-\,$  Stream-based processing of input images using either AXI4-Stream, AXI3 or AXI4

- Configuration through AXI4-Lite interface

- Output of disparity map starts before receiving the last pixel of both input images

- Support for variable image sizes

- Multi-clock design with faster clock for performance critical tasks

- Image rectification

- Rectification using a pre-computed compressed rectification map

- Bi-linear interpolation for subpixel accurate rectification

- Stereo matching

- Stereo matching through a variation of the Semi-Global Matching (SGM) algorithm

- Configurable disparity range from 32 to 256 pixels

- Configurable disparity offset

- Configurable penalties  $P_1$  and  $P_2$  for small and large disparity variations

- Edge-dependent variation of penalties

3. BACKGROUND CONTENTS

Pre-processing of input images for improved robustness against illumination variations and occlusions

#### Post-processing

- Subpixel optimization

- Consistency check with configurable threshold

- Uniqueness check with configurable threshold

- Filling of small gaps through interpolation

- Noise reduction

- Speckle filtering

- Filtering of untextured image areas

## 3 Background

### 3.1 Camera Alignment

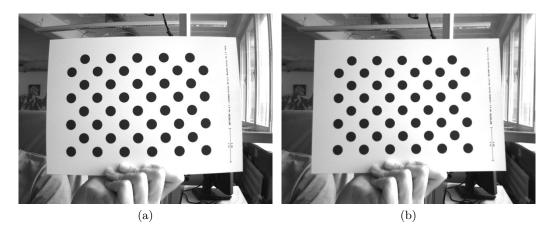

For stereo vision, both cameras must be mounted on a plane with a displacement that is perpendicular to the cameras' optical axes. Furthermore, both cameras must be equipped with lenses that have an identical focal length. This arrangement is known as the *standard epipolar geometry*. An example for such a camera mounting is shown in Figure 1.

The distance between both cameras is referred to as baseline distance. Using a large baseline distance improves the depth resolution at high distances. A small baseline distances, on the other hand, allows for the observation of close objects. The baseline distance should be adjusted in conjunction with the lenses' focal length. An online tool for computing desirable combinations of baseline distance and focal length can be found on the Nerian Vision GmbH website<sup>1</sup>.

#### 3.2 Image Rectification

Even when carefully aligning both cameras, you are unlikely to receive images that match the expected result form an ideal standard epipolar geometry. The images are affected by various distortions that result from errors in the cameras' optics and mounting. Therefore, the first processing step that needs to be performed is an image undistortion operation, which is known as *image rectification*.

<sup>&</sup>lt;sup>1</sup>https://nerian.com/support/resources/calculator/

Figure 1: Example for standard epipolar geometry.

3. BACKGROUND CONTENTS

Figure 2: Example for (a) unrectified and (b) rectified camera image.

Figure 2a shows an example camera image, where the camera was pointed towards a calibration board. The edges of the board appear slightly bent, due to radial distortions caused by the camera's optics. Figure 2b shows the same image after image rectification. This time, all edges of the calibration board are perfectly straight.

#### 3.3 Camera Calibration

Image rectification requires precise knowledge of the cameras' projective parameters, which is obtained through *camera calibration*. This typically requires the recording of several sample images of a flat calibration board with a visible calibration pattern. From the observed projection of this pattern it is then possible to compute the calibration parameters. This process is not implemented by the SVC, but has to be performed in software. Source code for computing the calibration parameters form a set of camera images is available.

#### 3.4 Disparity Maps

The stereo matching results are delivered by the SVC in the form of a disparity map, from the perspective of the reference camera. By default the left camera is the reference camera, but alternatively the right camera can be selected as reference camera during IP customization.

The disparity map associates each pixel in the reference camera image with a corresponding pixel in the other camera image (referred to as match camera). Because both images were previously rectified to match an ideal standard epipolar geometry, corresponding pixels should only differ in their horizontal coordinates. The disparity map thus only encodes a horizontal coordinate difference.

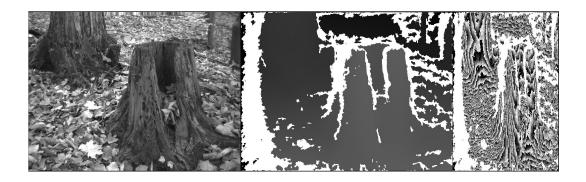

An example for a left camera image and the corresponding disparity map are shown in Figures 3a and 3b. Here the disparity map has been color coded, with blue hues reflecting small disparities, and red hues reflecting large disparities. As can be seen, the disparity is proportional to the inverse depth of the corresponding scene point.

Figure 3: Example for (a) left camera image and corresponding disparity map.

The disparity range specifies the image region that is searched for finding pixel correspondences. In the example image, the color legend indicates that the disparity range reaches from 0 to 111 pixels. A large disparity range allows for very accurate measurements, but causes a high computational load and thus lowers the achievable frame rate. The SVC supports a configurable disparity range, which provides a choice between high precision or high speed.

It is possible to transform the disparity map into a set of 3D points. This can be done at a correct metric scale if the cameras have been calibrated properly. The transformation of a disparity map to a set of 3D points requires knowledge of the disparity-to-depth mapping matrix Q, which can be computed during camera calibration. The 3D location  $\begin{pmatrix} x & y & z \end{pmatrix}^T$  of a point with image coordinates (u, v) and disparity d can be reconstructed as follows:

$$\begin{pmatrix} x \\ y \\ z \end{pmatrix} = \frac{1}{w} \cdot \begin{pmatrix} x' \\ y' \\ z' \end{pmatrix}, \text{ with } \begin{pmatrix} x' \\ y' \\ z' \\ w \end{pmatrix} = Q \cdot \begin{pmatrix} u \\ v \\ d \\ 1 \end{pmatrix}$$

An efficient implementation of this transformation is available in the API for the SceneScan stereo vision sensor.

The SVC computes disparity maps with a disparity resolution that is below one pixel. Disparity maps have a bit-depth of 12 bits, with the lower 4 bits of each value representing the fractional disparity component. It is thus necessary to divide each value in the disparity map by 16 in order to receive the correct disparity magnitude.

Several post-processing techniques are applied in order to improve the quality of the disparity maps. Some of these methods detect erroneous disparities and mark them as invalid. Invalid disparities are set to 0xFFF, which corresponds to the decimal value 255.9375 and is the maximum value that can be stored in the 12-bit disparity map. In Figure 3b invalid disparities have been depicted as black.

## 4 Stereo Vision Core Functionality

The overall functionality of the SVC is depicted in Figure 4. The port register\_io provides read and write access to the device registers, which keep all processing parameters. This port complies to the AXI4-Lite standard (ARM, 2013) and acts as a communication slave. The port frame\_complete provides a binary signal which is asserted to 1 for one clock cycle, once processing of the current frame has been completed.

The remaining input and output ports implement the AXI4-Stream protocol (ARM, 2010) and read image data and image rectification maps, or read and write temporary buffer data. The purpose of each port and the involved processing is described in the subsequent sections.

Processing inside the SVC is divided into several sub-modules. Not all of these sub-modules are mandatory. Some can be deactivated through setting the appropriate device registers, or they can be removed from the IP core altogether if desired. A detailed description of each sub-module is provided below.

## 4.1 Image Input and Output

The SVC can be parameterized to support different pixel formats. The supported formats are:

- 8-bit monochrome

- 12-bit monochrome

- RGB with 8 bits per color channel (24 bits in total)

Support for more than one pixel format can be activated during IP customization (see Section 6.1). If support for more than one pixel format is enabled, the data widths of all input and output ports that transport pixel data will be set to the pixel width of the largest pixel format. If a format with a shorter pixel width is used, then the unnecessary most significant bits will be ignored.

Even though an RGB color image provides more information than a grayscale image with equal spatial resolution, a color image will not lead to better processing results. However, the color information will be preserved during image rectification, and the rectified color image can hence be used for onward processing. If color information is not required for onward processing, it is recommended to disable support for RGB images and directly provide monochrome image data, as this can save significant FPGA resources.

During customization, a maximum image size must be specified that the SVC shall be able to handle. While the image height has only a marginal impact on the required FPGA resources, the image width will have a strong influence on the resource usage. In order to make the most efficient use of the available FPGA resources, the IP customization requires the configuration of the maximum *image row stride* rather than the image width. The row stride is the size of one image row in bytes, which depends on the selected pixel format. Hence, if the IP core is configured to support multiple pixel formats, then a different maximum image width is possible depending on the currently processed pixel format.

During customization, the IP core will determine the maximum image width from the configured row stride and pixel formats. The maximum width is the largest image width that can be realized with the smallest pixel format and the configured row stride. Further FPGA resources can be saved if the maximum image width can be constrained further than what would be possible with the configured row stride. Hence, it is possible to manually specify a smaller maximum image width during IP customization (see Section 6.1).

#### 4.2 Rectification

The SVC concurrently reads two input images from the left\_input and right\_input ports. The first processing step that is applied to the input data is image rectification. To perform image rectification, a pre-computed rectification map is required that is read from the dedicated input port rectification\_map. The rectification map contains a subpixel accurate x- and y-offset for each pixel of the left and right input images. Bi-linear interpolation is applied to map the subpixel offsets to image intensities.

The offsets are interleaved such that reading from a single data stream is sufficient for finding the displacement vector for each pixel in both images. To save bandwidth, the rectification map is stored in a compressed form. On average one byte is required for encoding the displacement vector for a single pixel. Hence, the overall size of the rectification map is equal to the size of two input images. Source code is provided for generating the rectification map from typical camera calibration parameters.

Rectification is a window-based operation. Hence, the pixel offsets are limited by the employed window size. In our recommended parameterization a window size of  $79 \times 79$  pixels is used. This allows for offsets in the range of -39 to +39 pixels. If desired, the window size can be adjusted to allow for larger pixel displacements.

The left rectified image is always written to left\_output, and the right rectified image to right\_output, unless the IP's operation mode has been set to passthrough, in which case the input mages are passed through without modification (see Section 11.2.1). Please note that the image that has been selected as reference image is output with a significantly higher latency than the match image.

#### 4.3 Image Pre-Processing

An image pre-processing method is applied to both input images. This causes the subsequent processing steps to be more robust towards illumination variations and occlusions.

#### 4.4 Stereo Matching

Stereo matching is performed by applying a variation of the SGM algorithm by Hirschmüller (2005). SGM applies two penalties  $P_1$  and  $P_2$  for solutions with small and large disparity variations. In our case, we adapt both penalties according to image edges. For both,  $P_1$  and  $P_2$ , there exist two different penalty values, which are applied to edge and non-edge image pixels. These penalties can be configured at run-time though the SVC's registers (see Section 11.2.12).

The SVC can require several iterations for processing one pixel of the reference input image. In each iteration, the reference image pixel is compared to a group of pixels in the match image. The number of parallel pixel comparisons p can be configured through the SVC customization parameters (see Section 6.1). The number of iterations per reference image pixel  $n_i$  can be configured through the SVC control register (see Section 11.2.1).

A disparity offset  $o_d$  can also be configured through the SVC's registers, which indicates the smallest disparity value that will be considered during stereo matching. If  $o_d \neq 0$  then the observable depth range will have an upper limit, as disparities smaller than  $o_d$  will not be allowed. The disparity offset  $o_d$ , iteration count  $n_i$  and the parallelization p determine the maximum disparity  $d_{max}$ :

$$d_{max} = o_d + n_i p - 1 \tag{1}$$

For storing intermediate processing results, the SGM sub-module requires write access to an external buffer through the port  $buffer_output$ . This buffer can be located in external memory, or if desired in the FPGA's block RAM. A lossy data compress is applied in order to reduce the required band-width and buffer size. The compression rate z can be configured during IP customization.

The total size  $s_b$  of the buffer can be computed as follows:

$$s_b = 3 \cdot (d_{max} - o_d + 1) \cdot w_{max} \cdot (1 - z) ,$$

(2)

where  $d_{max}$  is the maximum disparity and  $w_{max}$  is the maximum supported image width.

Data is written linearly to the buffer, starting from byte offset 0 all the way through to the last byte in the buffer. Once the last byte has been written, the SVC sends out a rewind signal. Writing will then restart again at byte offset 0. Similarly, the content of the same buffer is read back linearly through the port buffer\_input, and reading restarts at byte offset 0 upon a corresponding rewind signal. It is ensured that reading and writing will never happen simultaneously on the same buffer data.

#### 4.5 Cost Volume Post-Processing

The SGM stereo algorithm produces a *cost volume*, which encodes the matching costs for all valid combinations of left and right image pixels. Several of the applied post-processing techniques operate directly on this cost volume.

#### 4.5.1 Subpixel Optimization

Subpixel optimization is the first applied post-processing technique. This step increases the accuracy of depth measurements by evaluating the matching costs to the left and right of the detected minimum for each pixel. A curve is fitted to the matching costs and its minimum is determined with subpixel accuracy.

The optimization algorithm is tuned automatically to provide the best possible subpixel measurements. If only a small region of interest (ROI) of the input image / disparity map is relevant, then this auto-tuning process can be constrained to only this ROI. In this case one should expect more accurate sub-pixel measurements inside

the ROI. The ROI can be selected at run-time by writing to the SVC's registers (see Sections 11.2.13 and 11.2.14).

The improved disparity estimates are encoded as fixed-point numbers. Currently the SVC supports 4 decimal bits for the subpixel optimized disparity. Hence, it is possible to measure disparities with a resolution of ½16 pixel. It is thus required to divide each disparity value by 16, when interpreting the final disparity map.

#### 4.5.2 Uniqueness Check

Matches with a high matching uncertainty are discarded by imposing a uniqueness constraint. For a stereo match to be considered unique, the minimum matching cost  $c_{min}$  times a uniqueness factor  $q \in [1, \infty)$  must be smaller than the cost for the next best match. This relation can be expressed in the following formula, where C is the set of matching costs for all valid pixel pairs and  $c^* = c_{min}$  is the cost for the best match:

$$c^* \cdot q < \min \left\{ C \setminus \left\{ c_{\min} \right\} \right\}. \tag{3}$$

Stereo matches that are discarded through the uniqueness check are assigned a disparity label of 0xFFF.

#### 4.5.3 Consistency Check

A consistency check is employed for removing further matches with high matching uncertainties. The common approach to this post-processing technique is to repeat stereo matching in the opposite matching direction, and then only retaining matches for which

$$|d_r - d_m| \le t_c,\tag{4}$$

where  $d_r$  is the disparity from reference-to-match image matching,  $d_m$  the disparity from match-to-reference image matching, and  $t_c$  is the consistency check threshold.

In order to save FPGA resources, we refrain from re-running stereo matching a second time in the opposite matching direction. Rather, the match camera disparity map is inferred from the matching costs that have been gathered during the initial reference-to-match stereo matching. Pixels that do not pass the consistency check are again labeled with 0xFFF.

#### 4.6 Disparity Map Post-Processing

Following the cost volume post-processing, the cost volume is reduced to a disparity map (see Section 3.4). Additional post processing methods are then applied directly to the disparity values.

### 4.6.1 Texture Filtering

Matching image regions with little to no texture is particularly challenging. Especially if such regions occur close to image borders, this might lead to significant mismatches. In order to address this problem, a texture filter is applied. This filter computes a texture score  $s_t$  for each image pixel, which reflects the texture intensity within a local neighborhood. Pixels for which this score is below a configurable threshold  $t_t$  are again labeled with 0xFFF in the computed disparity map.

#### 4.6.2 Speckle Filtering

The aforementioned methods are not always able to identify and label all erroneous matches. Fortunately, the erroneous matches that remain tend to appear as small clusters of similar disparity. These speckles are then removed with a speckle filter. The speckle filter identifies connected components that are below a specified minimum size. The minimum speckle size is an IP core internal parameter that cannot be changed. However, it is possible to configure how many iterations of the speckle filter should be executed. A larger number of speckle filter iterations will result in larger speckles being removed. The pixels that belong to identified speckles are again labeled with 0xFFF.

#### 4.6.3 Gap Interpolation

The aforementioned post-processing techniques all remove pixels form the computed disparity map, which leaves gaps with no valid disparity data. If one such gap is small, it can be filled with valid disparities by interpolating the disparities from its edges. Interpolation is only performed for gaps whose vertical and horizontal extent  $l_h$  and  $l_v$  fulfill the condition

$$\min\left\{l_h, l_v\right\} \le l_{max},\tag{5}$$

where  $l_{max}$  is the maximum gap width. Interpolation is also omitted if the disparities from the edge of the identified gap do not have a similar magnitude.

#### 4.6.4 Noise Reduction

Finally, a noise reduction filter is applied to the generated disparity map. This filter performs a smoothing of the disparity map, while being aware of discontinuities and invalid disparities. If the operation mode is set to stereo matching (see Section 11.2.1), then the disparity map that results after this filter is directly written to the disparity\_output port.

## 5 DMA Core Functionality

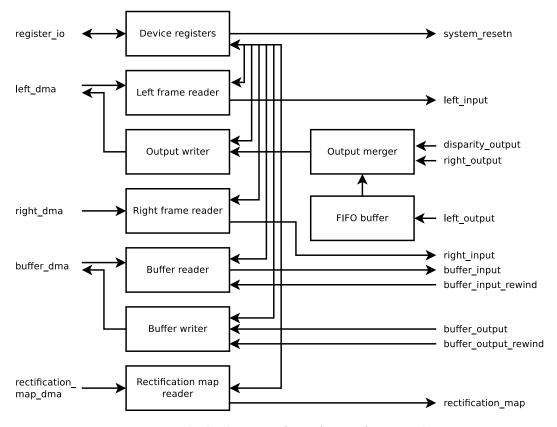

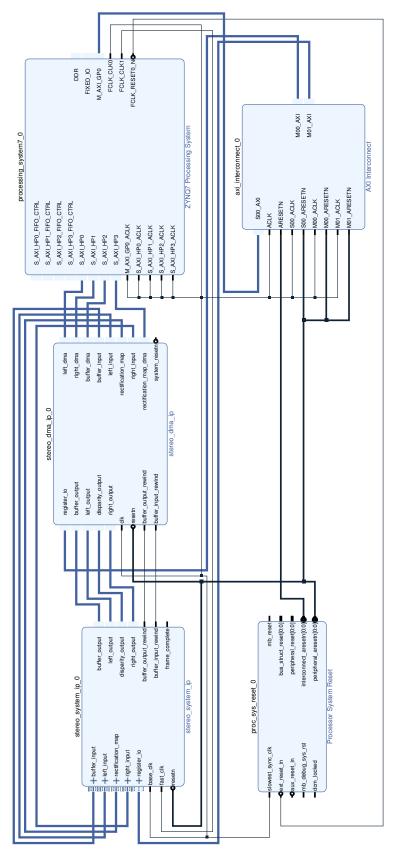

When using the SVC directly it is in the responsibility of the developer to provide all required data on the input ports and to collect the data from the output ports in time. In a typical setting, the input data is read from off-chip memory and the processing results are written back to memory. For systems with a shared system memory, such as the Zynq SoC, we provide a DMA core for fetching and writing data. The functionality of this core is depicted in the block diagram of Figure 5.

#### 5.1 Ports Connected to SVC

Except for the clock signals, the DMA core connects to all input and output ports of the SVC. In Figure 5, those ports are depicted on the right. The ports match the ones shown in Figure 4 on page 8, plus one further output and two inputs that were omitted previously for simplicity.

Figure 5: Block diagram of DMA core functionality.

The new output is system\_resetn, which is an active low reset signal. The reset signal is set to 0 if either the DMA core is reset itself, or if a soft reset is triggered through writing to the reset-bit in register 0x00. It is recommended that the SVC's reset input is connected to this output. Otherwise, the SVC will not be affected by a soft reset of the DMA core, which can lead to erroneous behavior.

The new SVC-specific input ports are buffer\_input\_rewind and buffer\_output\_rewind. These binary signals are asserted by the SVC when reading from or writing to the buffer memory shall restart from the beginning. It is important that reading does not start before this signal is asserted, as the relevant data might not yet have been written.

#### 5.2 Interface Ports

All ports that are not connected to the SVC appear on the left-hand side of Figure 5. The port register\_io provides read and write access to all device registers of the DMA core. This port complies to the AXI4-Lite standard (ARM, 2013) and acts as a communication slave.

The remaining ports follow the AXI3 or AXI4 standard (ARM, 2013) and act as communication masters. The left\_dma port fetches the left input image and is also used for delivering the processing results. Similarly, the right\_dma port is used for fetching the right input image. The port buffer\_dma serves for reading from and writing to the buffer memory and the rectification\_map\_dma port is used for

fetching the rectification map.

All fetch and write operations of the AXI3/AXI4 ports are controlled through the device registers. They contain the input and output memory addresses and can trigger read or write operations when set to a new value. More details on the device registers can be found in Section 11 on page 30.

#### 5.3 Input Formats

The DMA core can be configured to use a pixel width of 12 or 8 bits for monochrome images, or 8 bits per channel for RGB or Bayer pattern images (see Section 6.2). When set to 12-bit monochrome, different encoding options can be chosen for the input image data. The encoding mode can be selected at runtime by writing to the device registers (see Section 11.1.1).

#### 5.3.1 8-Bit Monochrome

In this mode, an 8-bit monochrome encoding is assumed for the input data, even if the DMA core has been configured for 12-bit pixel width. If this is the case, the most significant four bits of all pixels are set to 0.

#### 5.3.2 12-Bit Monochrome LSB Packed

In this encoding mode, two 12-bit values are written to 3 bytes in memory. This happens in a least-significant-bit (LSB) alignment, without introducing additional padding bits. This means that data is filled LSB first in the lowest byte, and then continues to higher addresses, as depicted below:

| 32        | 31 24           | 23 16             | 15 8              | 7 0             |

|-----------|-----------------|-------------------|-------------------|-----------------|

|           | Byte 3          | Byte 2            | Byte 1            | Byte 0          |

|           | Pixel 2         | Pixel 1           |                   | Pixel 0         |

| 11 10 9 8 | 7 6 5 4 3 2 1 0 | 11 10 9 8 7 6 5 4 | 3 2 1 0 11 10 9 8 | 7 6 5 4 3 2 1 0 |

This matches the Mono12p pixel format from the GenICam Pixel Format Naming Convention (European Machine Vision Association, 2016).

#### 5.3.3 12-Bit Monochrome GEV Packed

Like the previous mode, the 12-bit GEV packing mode encodes two 12-bit values in 3 bytes. In this case, the upper 8 bits of the first pixel are written to the first byte, and the upper 8 bits of the second pixel are written to the third byte. A combination of the lower 4 bits of both pixels are written to the second byte in between. This encoding scheme is depicted below:

| 24      | 23 16             | 15 8              | 7               | l .               |

|---------|-------------------|-------------------|-----------------|-------------------|

|         | Byte 3            | Byte 2            | Byte 1          | Byte 0            |

| Pixel 2 | Pixel 2           | Pixel 1           | Pixel 1 Pixel 0 | Pixel 0           |

| 3 2 1 0 | 11 10 9 8 7 6 5 4 | 11 10 9 8 7 6 5 4 | 3 2 1 0 3 2 1 0 | 11 10 9 8 7 6 5 4 |

This scheme matches the Mono12Packed format from the GigE Vision standard (AIA, 2013). The advantage of this encoding is that it can be efficiently converted to 8-bits, by leaving out every third byte from the image data.

#### 5.3.4 12-Bit Unpacked

In the unpacked 12-bit encoding mode, the image data is stored with 16 bits per pixel in memory. The DMA core ignores the most significant 4 bits of each pixel when reading the image data.

#### 5.3.5 8-Bit RGB

In the 8-bit RGB input mode the input image is a color image with 8 bits for each of the three color channels. Endianess does not matter for RGB images, which means that either the red or the blue color channel can be stored in the least or most significant bits. The green color channel, however, should be stored in the middle. The endianess of the output image will match the endianess of the input image. Either of the following encodings are hence possible:

| 24        | 23            |      |   |       |   |   |   | 16  | 15 |   |   |     |    |    |   | 8 | 7 |   |   |     |   |   |   | 0 |

|-----------|---------------|------|---|-------|---|---|---|-----|----|---|---|-----|----|----|---|---|---|---|---|-----|---|---|---|---|

|           |               |      | E | 3yt   | e | 2 |   |     |    |   | E | 3yt | e  | 1  |   |   |   |   | Ε | 3yt | e | 0 |   |   |

| Red LSB:  |               | Blue |   | Green |   |   |   | Red |    |   |   |     |    |    |   |   |   |   |   |     |   |   |   |   |

|           | 7             | 6    | 5 | 4     | 3 | 2 | 1 | 0   | 7  | 6 | 5 | 4   | 3  | 2  | 1 | 0 | 7 | 6 | 5 | 4   | 3 | 2 | 1 | 0 |

| Blue LSB: | SB: Red Green |      |   | Red   |   |   | 1 |     |    |   |   |     | Βl | ue |   |   |   |   |   |     |   |   |   |   |

|           | 7             | 6    | 5 | 4     | 3 | 2 | 1 | 0   | 7  | 6 | 5 | 4   | 3  | 2  | 1 | 0 | 7 | 6 | 5 | 4   | 3 | 2 | 1 | 0 |

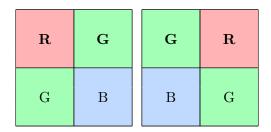

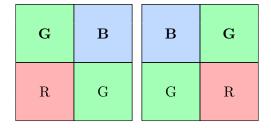

#### 5.3.6 8-Bit Bayer Pattern

As an alternative to using RGB encoding for color images, the DMA core can directly read 8-bit Bayer pattern images. The DMA core will then internally perform a Bayer pattern demosaicing and pass RGB encoded image data on to the SVC. In this mode, the DMA core will also downsample the input images by a factor of 2, meaning that the resulting RGB images will have half the original width and height. The downsampling is performed in order to minimize interpolation artifacts that will result from Bayer pattern demosaicing and which will affect the image processing. It is important that the SVC and DMA core are both configured to the size of the downsampled RGB image rather than the original Bayer pattern image size.

There exist 4 possible layouts of the Bayer pattern. We follow the GenICam Pixel Format Naming Convention (European Machine Vision Association, 2016) for differentiating them. The pattern layout can be identified by looking at the top left pixel and the pixel immediately to its right. The abbreviations of these two colors provide the name of the layout. The 4 possible pattern layouts are depicted in Figure 6.

Different patterns can be selected for the left and right camera images. This is necessary if the image sensors are not installed in the same orientation (e.g. one sensor being rotated by 180° relative to the other).

(a) RG Bayer pattern (b) GR Bayer pattern

(c) GB Bayer pattern (d) BG Bayer pattern

Figure 6: Possible Bayer pattern layouts.

Unlike when using RGB input images, endianess does matter for Bayer pattern processing. When performing demosaicing, the red component will be output to the least significant bits and the blue component to the most significant bits of the AXI stream. In memory, the the red component will be written to a lower address than the blue component. If the inverse byte order shall be used then this can be achieved by swapping the pattern layouts. In this case, RG and BG are swapped, as are GR and GB.

#### 5.4 Output Format Conversion

The rectified reference image and the disparity map that are output by the SVC are merged into a single data stream by the DMA core. This data stream is then output over the left\_dma port. Because the disparity map is computed with a significantly higher delay than the rectified reference image, the DMA core contains a sufficiently sized FIFO buffer for buffering the rectified reference image data.

In stereo matching mode, an image row of the (rectified) reference image and a row of the disparity map are output consecutively over the left\_dma port. When using pass-through or rectify mode, a row or the left and right images are output instead.

This interleaved output is repeated until there are no more remaining rows to be delivered. The resulting output data can thus be interpreted as a horizontal arrangement of the reference image and disparity map (or left and right image). This interpretation of the output data can be seen in Figure 7. For this example, the SVC and DMA-Core were configured to pass-through mode. The combined output image has thus twice the width of an original input image.

Before writing the data to memory, the DMA core can apply different conver-

sions to 12-bit data, such as for the disparity map or images with a 12-bit depth. Which conversion to apply can be selected when customizing the core. The available conversions are described in the following.

#### 5.4.1 12-Bit Packed Output

The 12-bit packed mode is the simplest conversion mode. In this case two 12-bit values are written to 3 bytes in memory. This happens without introducing additional padding bits. This encoding matches the 12-bit LSB packed encoding from Section 5.3.2.

#### 5.4.2 12-Bit Split Output

In this mode all 12-bit outputs are split into one 8-bit most-significant and one 4-bit least significant component. For the disparity map, the most-significant component matches the integer disparity, and the least-significant component matches the disparity decimal bits (see Section 4.5.1). These two components are combined into two new images, which are output separately, again in a row-wise interleaving.

It has to be considered that an element of the least-significant component map only has a size of 4-bits. Hence, two consecutive values are combined into a single byte. For this operation the first 4-bit element is written to the less-significant 4 bits, and the second element is written to the more-significant 4 bits of the 8-bit output value.

An example for the output of the DMA core with 12-bit split output, when processing 8-bit input images for stereo matching, is shown in Figure 8. In this case, the merged output data can be interpreted as a row-wise sampled image with dimensions  $2.5w \times h$ , where w and h are the width and height of the input image. As can be seen, the output image is a horizontal arrangement of the rectified reference image, the integer disparity map and the subpixel component map.

#### 5.4.3 16-Bit Output

If the 16-bit output is selected, all 12-bit values are inflated to 16 bits and written to two bytes in memory. This happens by introducing additional high-significant bits,

Figure 7: Example for merged output with two 8-bit images.

Figure 8: Example for merged output with 12-bit split encoding.

which are set to 0. This matches the 12-bit unpacked encoding from Section 5.3.4.

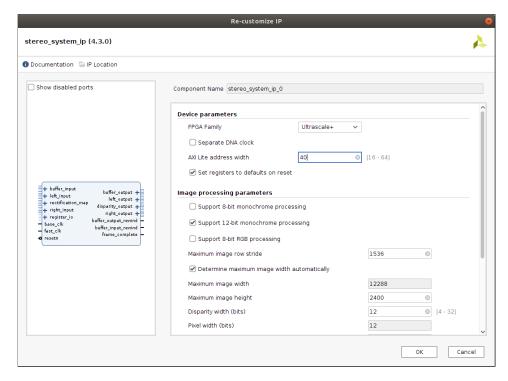

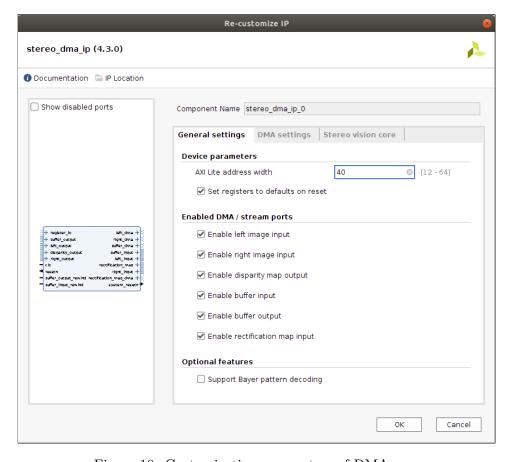

#### 6 Customization

Both, the SVC and the DMA core can be customized through several parameters. In Vivado's IP Integrator, these parameters can be set through the customization GUI. Screenshots of the customization windows for the SVC and DMA core are provided in Figures 9 and 10. Further parameters might be available for modification upon request. Please contact us if you have any special requirements.

#### 6.1 SVC Customization Parameters

The SVC provides the customization parameters listed below. For some parameters a recommended value is provided, which we advise and use in our own products. All performance indicators that are provided in this document have been obtained with the recommended parameterization.

**FPGA Family:** Needs to be set to UltraScale+ or 7-series, depending on for which FPGA the IP core should be synthesized.

Separate DNA clock: If enabled, the separate input clock dna\_clk will be used for accessing the DNA port. This option is necessary if the base clock frequency does not match the clock frequency of the DNA port (typically 100 MHz). This clock must not be connected to the same source as base\_clk or fast\_clk, as a false path constraint between these clocks is automatically generated.

**AXI Lite address width:** Width in bits of an address for the register\_io port. This should be 32 for Zynq-7000 devices and 40 for Zynq UltraScale+ devices.

**Set registers to defaults on reset:** If enabled, the internal configuration registers will be reset to their default values when the active-low reset signal is asserted to 0.

**Support 8-bit monochrome processing:** If enabled, the IP is able to process input images in 8-bit monochrome encoding.

Figure 9: Customization parameters of SVC.

Figure 10: Customization parameters of DMA core.

- **Support 12-bit monochrome processing:** If enabled, the IP is able to process input images in 12-bit monochrome encoding

- **Support 8-bit RGB processing:** If enabled, the IP is able to process input images in RGB encoding with 8 bits per color channel (24 bits in total).

- Maximum image row stride: The maximum supported row stride for an input image (see Section 4.1. This parameter has a significant impact on the block RAM usage. Recommended value for Zynq Z-7020: 800; recommended value for Zynq UltraScale+ ZU3: 1536.

- **Determine maximum image width automatically:** If enabled, the maximum image width will be determined automatically from the configured row stride and pixel format. Please refer to Section 4.1 for further information.

- Maximum image width: If the option 'determine maximum image width automatically' is not enabled, then the maximum image width can be specified here. The maximum width must be smaller than the automatically determined value. The actual image width is configured through the SVC registers and can be smaller (see Section 11.2.2).

- **Maximum image height:** Maximum allowed height  $h_{max}$  of an input image. The actual image height is configured through the SVC registers at runtime (see Section 11.2.2). This parameter only has a small impact on the resource usage. The value must be a multiple of the internal buffer size.

- **Disparity width:** The bit width of the output disparity map. This value must be large enough to allow for an output of the maximum disparity for the current parameterization. Please keep in mind that the disparities contain a 4-bit subpixel component (see Section 3.4). Recommended value: 12.

- **Pixel width:** The bit width of one input pixel. This parameter inferred automatically from the enabled pixel formats.

- Maximum rectification displacement: The maximum offset that a pixel can be moved in vertical or horizontal direction during image rectification (see Section 4.2). This parameter has a significant impact on the block RAM usage. If a value of 0 is provided, then image rectification is disabled. Please note that the provided rectification map must be computed with respect to this parameter.

- Number of pixels processed in parallel: The number of pixels p that are compared in parallel during SGM stereo matching. Together with the number of iterations, this parameter defines the disparity range (see Section 4.4). This parameter has a significant impact on the LUT usage. Recommended value for Zynq Z-7020: 16; recommended value for Zynq UltraScale+ ZU3: 32.

- Maximum number of iterations per pixel: SGM stereo matching requires several iterations for processing a single pixel of the left input image (see Section 4.4). This parameter defines the maximum number of iterations that are allowed to be performed. Together the number of iterations and number of pixels

processed in parallel define the disparity range. A lower number of iterations can be configured at runtime by writing to the SVC's registers (see Section 11.2.1). Recommended value for Zynq Z-7020: 16; recommended value for Zynq UltraScale+ ZU3: 8.

- Optimize for low iteration count: If the IP core is configured for only few iterations per pixel, then the image processing will not be very efficient. In this case, additional buffers will be needed in order to guarantee a non-interrupted processing. These buffers are instantiated if this option is enabled. Please be aware that enabling this option will increase the block RAM usage. It is recommended to enable this option if the iteration count is less than 4, but even for higher iteration counts enabling this option can significantly improve the performance.

- Maximum speckle filter iterations: In order to remove more speckles, the IP core can be configured to run multiple iterations of the speckle filter (see 4.6.2). The maximum number of iterations must be configured during customization. Increasing the maximum number of iterations will cause a moderate increase of the required FPGA resources.

- Internal processing buffer size: Size of an internal buffer that is used by SGM stereo matching for caching computation results. This parameter has a high impact on the LUT and block RAM usage. Increasing this parameter significantly reduces the bandwidth that is required for reading from / writing to the external buffer. Recommended value: 16.

- External processing buffer compression: A lossy data compression that is applied to the external buffer (see Section 4.4). Recommended values are 0% to 37.5%.

- Matching direction: Specifies the direction in which stereo matching shall be performed. If 'left to right' is selected, then the left image will be the reference image and the right image will be the match image. If 'right to left' is selected, then the roles will be reversed. Default value: 'left to right'.

- **Enable debugging registers:** If enable, the SVC will hold additional registers with debugging information at the end of the register address space (see Section 11.2.16). These registers are intended for analysis by Nerian's technical support team. Enabling this option will cause a slight increase in resource usage.

#### 6.2 DMA Core Customization Parameters

Most of the SVC customization parameters are also available in the DMA core, on the *stereo vision core* settings page. It is important that these common parameters are configured identically in both cores. On top of the SVC parameters, the DMA core also provides its own customization parameters.

#### 6.2.1 General Settings

- **AXI Lite address width:** Width in bits of an address for the register\_io port. This should be 32 for Zynq-7000 devices and 40 for Zynq UltraScale+ devices.

- Set registers to defaults on reset: If enabled, the internal configuration registers will be reset to their default values when the active-low reset signal is asserted to 0.

- **Enable ... input/output:** The AXI Stream input and output ports can be enabled or disabled individually. If a port is not required, then FPGA resources can be saved by disabling it.

- **Support Bayer pattern decoding:** If enabled, the DMA core can perform a Bayer pattern demosaicing through subsampling, while reading an input image (see Section 5.3.6).

#### 6.2.2 DMA Settings

- Buffer DMA AXI version: AXI protocol version for the buffer\_dma port. This should be AXI3 for Zynq-7000 devices and AXI4 for Zynq UltraScale+ devices.

- Buffer DMA address width: Width in bits of an address for the buffer\_dma port. This should be 32 for Zynq-7000 devices and 49 for Zynq UltraScale+devices.

- Buffer DMA burst size: Width in bits of a data word for the buffer\_dma port. This interface will be subject to high bandwidth data transfers. It should thus be configured to the highest data width that is supported by the external memory. This should be 64 for Zynq-7000 devices and 128 for Zynq UltraScale+devices.

- Buffer DMA burst length: Number of data transfers in one burst for the buffer\_dma port. Recommended value for Zynq Z-7020: 16; recommended value for Zynq UltraScale+ ZU3: 32.

- Buffer maximum concurrent write bursts: Maximum allowed number of outstanding write bursts for the buffer\_dma port. Recommended value: 4.

- Buffer maximum concurrent read bursts: Maximum allowed number of outstanding read bursts for the buffer\_dma port. Recommended value: 4.

- Buffer write FIFO size: Size of the FIFO buffer that is attached to the write channel of the buffer\_dma port, measured in data words. Recommended value for Zynq Z-7020: 16; recommended value for Zynq UltraScale+ ZU3: 8.

- Buffer read FIFO size: Size of the FIFO buffer that is attached to the read channel of the buffer\_dma port, measured in data words. Recommended value for Zynq Z-7020: 16; recommended value for Zynq UltraScale+ ZU3: 8.

- Other DMA AXI version: AXI protocol version for all ports other than buffer\_dma. This should be AXI3 for Zynq-7000 devices and AXI4 for Zynq UltraScale+devices.

Table 1: SVC processing delays for default parameterization when processing input images of size  $640 \times 480$  pixels and 128 disparity levels.

| Delay                    | Fast clock cycles | Time                 |

|--------------------------|-------------------|----------------------|

| Delay until first output | 236,000           | $0.78 \mathrm{\ ms}$ |

| Delay until last output  | 2,297,000         | $7.66~\mathrm{ms}$   |

- Other DMA address width: Width in bits of an address for all ports other than buffer\_dma. This should be 32 for Zynq-7000 devices and 49 for Zynq Ultra-Scale+ devices.

- Other DMA burst size: Width in bits of a data word for all ports other than buffer\_dma. This should be 64 for Zynq-7000 devices and 128 for Zynq UltraScale+ devices.

- Other DMA burst length: Number of data transfers in one burst for all ports other than buffer\_dma. Recommended value for Zynq Z-7020: 16; recommended value for Zynq UltraScale+ ZU3: 32.

- 12-bit encoding mode: The DMA core provides several ways for encoding 12-bit output data, such as the disparity map. Please refer to Section 5.4 for a description of the available encoding modes.

## 7 Supported Devices

The SVC has been field-tested on the Zynq-7000 and Zynq UltraScale+ SoCs. We thus recommend using these FPGA families. However, our IP core is also compatible to other Xilinx 7-Series and UltraScale+ devices. Please contact us to find out if your desired device is supported.

## 8 Timing

The SVC has been implemented as a multi-clock design. All input and output signals are associated with the *base clock*. When synthesized for the Zynq-7000 or Zynq UltraScale+ SoC with speed grade 1, the recommended frequency for this clock is 100 MHz. In addition to the base clock, the SVC uses the so-called *fast clock* for clocking particularly performance critical tasks. The recommended frequency for this clock is 143 MHz for a Zynq 7000 SoC, and 300 MHz for a Zynq Ultrascale+ SoC with speed grade 1. The IP core will add a false path constraint between both clock domains.

If the DMA core is employed, its clock input has to be connected to the base clock. The recommended clock speed of the base clock matches the clock speed for the Zynq-7000 and UltraScale+ AXI memory interfaces. Hence, the DMA core can be directly connected to the Zynq's AXI slave ports.

The expected SVC processing delays when processing an input image of resolution  $640 \times 480$  pixels with the recommended parameterization for the Zynq UltraScale+ ZU3 (32 times parallelization; see Section 6) and 4 iterations per pixel

Table 2: SVC and DMA core customization parameters for resource usage evaluation.

| Customization parameter                | Value         |

|----------------------------------------|---------------|

| Support 8-bit monochrome processing    | yes           |

| Support 12-bit monochrome processing   | yes           |

| Support 8-bit RGB processing           | yes           |

| Maximum image row stride               | 1536          |

| Maximum image width                    | 1024          |

| Maximum image height                   | 8096          |

| Disparity width (bits)                 | 12            |

| Maximum rectification displacement     | 39            |

| Number of pixels processed in parallel | 32            |

| Maximum number of iterations per pixel | 8             |

| Optimize for low iteration count       | no            |

| Maximum speckle filter iterations      | 2             |

| Internal processing buffer size        | 16            |

| External processing buffer compression | 37.5%         |

| Matching direction                     | left to right |

| Enable debugging registers             | no            |

| Buffer maximum concurrent write bursts | 4             |

| Buffer maximum concurrent read bursts  | 4             |

| Buffer write FIFO size                 | 16            |

| Buffer read FIFO size                  | 16            |

| 12-bit encoding mode                   | 12-bit packed |

| Support Bayer pattern decoding         | yes           |

(i.e. 128 disparity levels) are listed in Table 1. The delays are given for a 100 MHz base clock and a 300 MHz fast clock, and are measured from the moment at which the first data item arrives at the SVC. As first output we consider the first byte of the computed disparity map. Consequently, the last output is the last byte of the disparity map, after which processing is complete.

The measurements were determined under the assumption that new data is always available at the SVCs inputs. If the data to be processed is read from system memory, higher delays might occur due to the additional memory delays.

## 9 Resource Usage

Table 2 contains our recommended customization parameters when synthesizing the IP core for a Zynq UtraScale+ ZU3. The resource usage of the SVC and DMA Core when synthesizing with these parameters is shown in Table 3. The table further contains resource usage information for the individual sub-modules that have been identified in Section 4. These numbers provide an overview of the gains that can be achieved when removing one of the sub-modules from the SVC.

| Description           | Slice LUTs | Registers | Memory | DSPs |

|-----------------------|------------|-----------|--------|------|

| SVC total usage       | 48,022     | 57,247    | 161.5  | 56   |

| DMA core total usage  | 7,219      | 8,740     | 8.5    | 6    |

| Image rectification   | 6,048      | 3,171     | 66.0   | 28   |

| Image pre-processing  | 498        | 1,264     | 4.0    | 2    |

| SGM stereo            | 22,809     | 36,104    | 60.0   | 0    |

| Subpixel optimization | 2,284      | 2,112     | 0.0    | 1    |

| Uniqueness check      | 852        | 811       | 0.0    | 1    |

| Consistency check     | 3,887      | 3,141     | 1.0    | 0    |

| Texture filter        | 558        | 966       | 16.5   | 3    |

| Speckle filter        | 7,675      | 5,308     | 7.0    | 2    |

| Gap interpolation     | 1,026      | 1,289     | 4.0    | 6    |

| Noise suppression     | 825        | 1,122     | 1.0    | 1    |

| Others                | 1,560      | 1,959     | 2.0    | 12   |

|                       |            | •         | •      | •    |

Table 3: Resource usage of SVC and individual sub-modules.

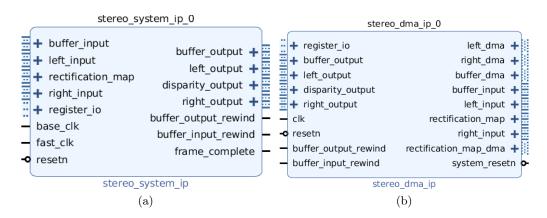

Figure 11: Interfaces of (a) SVC and (b) DMA core as shown by IP Integrator.

## 10 IO Signals

Figures 11a and 11b show a depiction of the SVC and DMA core as they appear in IP Integrator, which is part of Xilinx Vivado. Most of the shown ports have already been described in Sections 4 and 5. A detailed list of all input and output signals, including a breakdown of the AXI ports, is provided in Table 4 for the SVC. Likewise, Table 5 contains an equivalent list for the DMA core.

Table 4: List of SVC input and output signals..

| Signal name | i/o | Bits | Description                             |

|-------------|-----|------|-----------------------------------------|

| base_clk    | i   | 1    | Base clock source; this is the relevant |

|             |     |      | clock for all input and output signals  |

|             |     |      | (see Section 8)                         |

| $fast\_clk$ | i   | 1    | A faster clock for performance criti-   |

|             |     |      | cal tasks (see Section 8)               |

| $ m dna\_clk$     | i | 1 | Separate clock used for accessing the |

|-------------------|---|---|---------------------------------------|

|                   |   |   | DNA port. This clock input is op-     |

|                   |   |   | tional (see Section 6.1)              |

| resetn            | i | 1 | Global reset signal; active low       |

| $frame\_complete$ | О | 1 | Signals that processing of the cur-   |

|                   |   |   | rent frame has finished (see Sec-     |

|                   |   |   | tion 4)                               |

## register\_io signals

| register_io signals    |   |          |                                     |  |  |  |  |  |

|------------------------|---|----------|-------------------------------------|--|--|--|--|--|

| register_io_araddr     | i | variable | Read address                        |  |  |  |  |  |

| register_io_arprot     | i | 3        | Protection type; ignored!           |  |  |  |  |  |

| register_io_arready    | О | 1        | Read address ready; always 1!       |  |  |  |  |  |

| register_io_arvalid    | i | 1        | Read address valid                  |  |  |  |  |  |

| register_io_awaddr     | i | variable | Write address                       |  |  |  |  |  |

| register_io_awprot     | i | 3        | Protection type; ignored!           |  |  |  |  |  |

| register_io_awready    | О | 1        | Write address ready; always 1!      |  |  |  |  |  |

| register_io_awvalid    | i | 1        | Write address valid                 |  |  |  |  |  |

| register_io_bready     | i | 1        | Response ready                      |  |  |  |  |  |

| register_io_bresp      | О | 2        | Write response; always $00_2$ (OK)! |  |  |  |  |  |

| register_io_bvalid     | О | 1        | Write response valid                |  |  |  |  |  |

| register_io_rdata      | О | 32       | Read data                           |  |  |  |  |  |

| register_io_rready     | i | 1        | Read ready                          |  |  |  |  |  |

| register_io_rresp      | О | 2        | Read response; always $00_2$ (OK)!  |  |  |  |  |  |

| register_io_rvalid     | О | 1        | Read valid                          |  |  |  |  |  |

| register_io_wdata      | i | 32       | Write data                          |  |  |  |  |  |

| register_io_wready     | О | 1        | Write ready                         |  |  |  |  |  |

| register_io_wstrb      | i | 4        | Write strobes; ignored!             |  |  |  |  |  |

| $register\_io\_wvalid$ | i | 1        | Write valid                         |  |  |  |  |  |

|                        |   |          |                                     |  |  |  |  |  |

## Signals for AXI4-Stream inputs

| Signals for AX14-Stream inputs |   |          |                                     |  |  |  |

|--------------------------------|---|----------|-------------------------------------|--|--|--|

| left_input_tready              | О | 1        | Ready to receive left image         |  |  |  |

| $left\_input\_tvalid$          | i | 1        | Left image data is valid            |  |  |  |

| left_input_tdata               | i | variable | Left image data                     |  |  |  |

| $right\_input\_tready$         | О | 1        | Ready to receive right image        |  |  |  |

| $right\_input\_tvalid$         | i | 1        | Right image data is valid           |  |  |  |

| $right\_input\_tdata$          | i | variable | Right image data                    |  |  |  |

| $rectification\_map\_tready$   | О | 1        | Ready to receive rectification map  |  |  |  |

| $rectification\_map\_tvalid$   | i | 1        | Rectification map data is valid     |  |  |  |

| $rectification\_map\_tdata$    | i | 32       | Rectification map data              |  |  |  |

| buffer_input_rewind            | О | 1        | Reading from buffer shall restart   |  |  |  |

|                                |   |          | from offset 0 (see Sections 4.4 and |  |  |  |

|                                |   |          | 5.1)                                |  |  |  |

| buffer_input_tready            | О | 1        | Ready to receive buffer input       |  |  |  |

| buffer_input_tvalid            | i | 1        | Buffer input data is valid          |  |  |  |

| $buffer\_input\_tdata$         | i | variable | Buffer input data                   |  |  |  |

|                                |   |          |                                     |  |  |  |

Signals for AXI4-Stream outputs  ${\bf S}_{\bf S}$

| left_output_tready          | i | 1        | Ready to deliver left output             |

|-----------------------------|---|----------|------------------------------------------|

| left_output_tvalid          | О | 1        | Left output data is valid                |

| left_output_tdata           | О | variable | Left output data                         |

| $right\_output\_tready$     | i | 1        | Ready to deliver left output             |

| $right\_output\_tvalid$     | О | 1        | Left output data is valid                |

| $right\_output\_tdata$      | О | variable | Left output data                         |

| $disparity\_output\_tready$ | i | 1        | Ready to deliver disparity output        |

| $disparity\_output\_tvalid$ | О | 1        | Disparity output data is valid           |

| $disparity\_output\_tdata$  | О | variable | Disparity output data                    |

| buffer_output_rewind        | О | 1        | Writing to buffer shall restart from     |

|                             |   |          | offset 0 (see Sections $4.4$ and $5.1$ ) |

| buffer_output_tready        | i | 1        | Ready to deliver buffer output           |

| $buffer\_output\_tvalid$    | О | 1        | Buffer output data is valid              |

| $buffer\_output\_tdata$     | o | variable | Buffer output data                       |

Table 5: List of DMA core input and output signals.

| Signal name                                       | i/o | Bits                    | Description                                  |  |

|---------------------------------------------------|-----|-------------------------|----------------------------------------------|--|

| clk                                               | i   | 1                       | Main clock source; has to match the base     |  |

|                                                   |     |                         | clock from SVC                               |  |

| resetn                                            | i   | 1                       | Global reset signal; active low              |  |

|                                                   |     | •                       | •                                            |  |

|                                                   |     | $\operatorname{regist}$ | er_io signals                                |  |

| $register\_io\_araddr$                            | i   | variable                | Read address                                 |  |

| ${\tt register\_io\_arprot}$                      | i   | 3                       | Protection type; ignored!                    |  |

| $register\_io\_arready$                           | О   | 1                       | Read address ready; always 1!                |  |

| $register\_io\_arvalid$                           | i   | 1                       | Read address valid                           |  |

| $register\_io\_awaddr$                            | i   | variable                | Write address                                |  |

| $register\_io\_awprot$                            | i   | 3                       | Protection type; ignored!                    |  |

| register_io_awready                               | О   | 1                       | Write address ready; always 1!               |  |

| $register\_io\_awvalid$                           | i   | 1                       | Write address valid                          |  |

| $register\_io\_bready$                            | i   | 1                       | Response ready                               |  |

| $register\_io\_bresp$                             | О   | 2                       | Write response; always 00 <sub>2</sub> (OK)! |  |

| $register\_io\_bvalid$                            | О   | 1                       | Write response valid                         |  |

| $register\_io\_rdata$                             | О   | 32                      | Read data                                    |  |

| $register\_io\_rready$                            | i   | 1                       | Read ready                                   |  |

| $register\_io\_rresp$                             | О   | 2                       | Read response; always $00_2$ (OK)!           |  |

| $register\_io\_rvalid$                            | О   | 1                       | Read valid                                   |  |

| $register\_io\_wdata$                             | i   | 32                      | Write data                                   |  |

| $register\_io\_wready$                            | О   | 1                       | Write ready                                  |  |

| $register\_io\_wstrb$                             | i   | 4                       | Write strobes; ignored!                      |  |

| $register\_io\_wvalid$                            | i   | 1                       | Write valid                                  |  |

|                                                   |     |                         |                                              |  |

| buffer_io / left_io / right_io / rect_map signals |     |                         |                                              |  |

| '            | builei_io / i | ert_10 / | right_io / rect_map signals                     |

|--------------|---------------|----------|-------------------------------------------------|

| $*$ _araddr  | О             | variable | Read address                                    |

| $*$ _arburst | О             | 2        | Read burst type; always 01 <sub>2</sub> (INCR)! |

| $*$ _arcache | О | 4        | Read memory type; always $0011_2$ (normal,           |

|--------------|---|----------|------------------------------------------------------|

|              |   |          | non-cacheable, bufferable)!                          |

| $*$ _arlen   | О | variable | Read burst length                                    |

| $*$ _arlock  | О | 2        | Read lock type; always $00_2$ (normal acces)!        |

| $*$ _arprot  | О | 3        | Read protection type; always 000 <sub>2</sub> (un-   |

|              |   |          | privileged secure data)!                             |

| $*\_arqos$   | О | 4        | Read quality of service; always 0000 <sub>2</sub> !  |

| $*$ _arready | i | 1        | Read ready                                           |

| $*$ _arsize  | О | 3        | Read burst size; always 011 <sub>2</sub> (8 bytes)!  |

| $*$ _arvalid | О | 1        | Read valid                                           |

| $*$ _awaddr  | О | 32       | Write address                                        |

| $*$ _awburst | О | 2        | Write burst type; always 01 <sub>2</sub> (INCR)!     |

| $*$ _awcache | О | 4        | Write memory type; always 0011 <sub>2</sub> (nor-    |

|              |   |          | mal, non-cacheable, bufferable)!                     |

| $*$ _awlen   | О | variable | Write burst length                                   |

| $*$ _awlock  | О | 2        | Write lock type; always 00 <sub>2</sub> (normal ac-  |

|              |   |          | ces)!                                                |

| $*$ _awprot  | О | 3        | Write protection type; always $000_2$ (un-           |

|              |   |          | privileged secure data)!                             |

| *_awqos      | О | 4        | Write quality of service; always 0000 <sub>2</sub> ! |

| $*$ _awready | i | 1        | Write address ready                                  |

| $*$ _awsize  | О | 3        | Write burst size; always 011 <sub>2</sub> (8 bytes)! |

| $*$ _awvalid | О | 1        | Write address valid                                  |

| $*$ _bready  | О | 1        | Write response ready; always 1!                      |

| $*\_{bresp}$ | i | 2        | Write response                                       |

| $*$ _bvalid  | i | 1        | Write response valid                                 |

| $*$ _rdata   | i | variable | Read data                                            |

| $*$ _rlast   | i | 1        | Read last                                            |

| $*$ _rready  | О | 1        | Read ready                                           |

| $*$ _rresp   | i | 2        | Read response                                        |

| $*$ _rvalid  | i | 1        | Read last                                            |

| $*$ _wdata   | О | variable | Write data                                           |

| $*$ _wlast   | О | 1        | Write last                                           |

| $*$ _wready  | i | 1        | Write ready                                          |

| $*$ _wstrb   | О | 8        | Write strobes; always 111111111 <sub>2</sub> !       |

| *_wvalid     | О | 1        | Write valid                                          |

|              | ļ | ı        | 1                                                    |

## left\_input / right\_input / rectification\_map / buffer\_input signals

| *_ready | i | 1      | Ready to deliver input data |

|---------|---|--------|-----------------------------|

| *_valid | О | 1      | Input data valid            |

| *_data  | О | varied | Data directed to SVC        |

# $left\_output \ / \ right\_output \ / \ disparity\_output \ / \ buffer\_ \ output \ signals$

| $*$ _ready | О | 1      | Ready to receive output data |

|------------|---|--------|------------------------------|

| *_valid    | i | 1      | Output data is valid         |

| *_data     | i | varied | Data received from SVC       |

####

## 11 Registers

The SVC and DMA core each hold several registers that control the device behavior and provide information about the internal device state. Both IP cores have their own address spaces, starting at address 0x00. Please note that only the least significant address bits are evaluated and that reading from / writing to higher addresses will still affect the device registers.

A complete list of all available registers is shown in Table 6 for the SVC, and in Table 7 for the DMA core. All registers that have been marked with r are read-only. Writing to these registers will not produce an error but the new data is ignored.

Each register has a size of 32 bits. To simplify access from a CPU, the register addresses are always multiples of 4. Read and write operations must always be aligned to a 4-byte boundary. Reading from or writing to an address that is not a multiple of 4 is disallowed and has an undefined outcome. In the following, a description of all SVC and DMA core registers is provided, sorted by register address.

Table 6: Address space for SVC registers.

| Address(es) | Name                             | Read/Write |

|-------------|----------------------------------|------------|

| 0x00        | Control                          | r/w        |

| 0x04        | Image size                       | r/w        |

| 0x08        | Algorithm parameters 1           | r/w        |

| 0x0C        | Algorithm parameters 2           | r/w        |

| 0x10        | License key higher 32 bits       | r/w        |

| 0x14        | License key middle 32 bits       | r/w        |

| 0x18        | License key lower 32 bits        | r/w        |

| 0x1C        | Device DNA higher 32 bits        | r          |

| 0x20        | Device DNA middle 32 bits        | r          |

| 0x24        | Device DNA lower 32 bits         | r          |

| 0x28        | SVC errors                       | r          |

| 0x2C        | SGM penalties                    | r/w        |

| 0x30        | Subpixel optimization ROI offset | r/w        |

| 0x34        | Subpixel optimization ROI size   | r/w        |

| 0x38        | IP version number                | r          |

| 0x3C-0x90   | Debugging registers              | r          |

Table 7: Address space for DMA registers.

| Address | Name                                     | Read/Write |

|---------|------------------------------------------|------------|

| 0x00    | Control                                  | r/w        |

| 0x04    | Status                                   | r          |

| 0x08    | Image size                               | r/w        |

| 0x0C    | Output address higher 32 bits            | r/w        |

| 0x10    | Output address lower 32 bits             | r/w        |

| 0x14    | Output bytes available                   | r          |

| 0x18    | Output FIFO info                         | r          |

| 0x1C    | Left input address higher 32 bits        | r/w        |

| 0x20    | Left input address lower 32 bits         | r/w        |